155ТМ7 — различия между версиями

Hdc (обсуждение | вклад) (Новая страница: «Микросхема ТМ7 содержит четыре D-триггера, входы синхронизации которых попарно соединен…») |

Hdc (обсуждение | вклад) |

||

| (не показано 7 промежуточных версии этого же участника) | |||

| Строка 6: | Строка 6: | ||

Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы | Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы | ||

| − | Каждый триггер микросхемы имеет прямые Q и инверсные {{Overline|Q} выходы. | + | Каждый триггер микросхемы имеет прямые Q и инверсные {{Overline|Q}} выходы. |

| + | |||

| + | Основные параметры микросхемы: | ||

| + | |||

| + | Напряжение питания: 5 В;<br /> | ||

| + | Выходное напряжение логического нуля <= 0,4 В;<br /> | ||

| + | Выходное напряжение логической единицы >= 2,4 В;<br /> | ||

| + | Входной ток логического нуля <= -3,2 мА (вх. 2, 3, 6, 7), -6.4 мА;<br /> | ||

| + | Входной ток логической единицы <= 0,16 мА;<br /> | ||

| + | Время распространения импульса при переходе 0 - 1 <= 25 нс;<br /> | ||

| + | Время распространения импульса при переходе 1 - 0 <= 30 нс;<br /> | ||

| + | Потребляемый от источника питания ток <= 53 мА. | ||

| + | |||

| + | Функциональная схема: | ||

| + | |||

| + | [[File:tm7.png]] | ||

| + | |||

| + | Структура D-триггера: | ||

| + | |||

| + | [[File:tm7_structure.png]] | ||

| + | |||

| + | |||

| + | Временные диаграммы: | ||

| + | |||

| + | [[File:tm7_timings.png]] | ||

| + | |||

| + | {| class="wikitable" align="center" | ||

| + | |+Состояния триггеров ТМ7 | ||

| + | |- | ||

| + | ! rowspan="2" | Режим работы!! colspan="2" | Входы!! colspan="2" | Выходы | ||

| + | |- | ||

| + | ! EI !! D !! Q<sup>n+1</sup> !! {{overline|Q}}<sup>n+1</sup> | ||

| + | |- | ||

| + | | rowspan="2" align="left" | Разрешение передачи данных на выход ||1 || 0 || 0 || 1 | ||

| + | |- | ||

| + | | 1 || 1 || 1 || 0 | ||

| + | |- | ||

| + | | align="left" | Защёлкивание данных || 0 || * || Q<sup>n</sup> = 1 || {{overline|Q}}<sup>n</sup> = 0 | ||

| + | |} | ||

Текущая версия на 18:21, 21 июля 2012

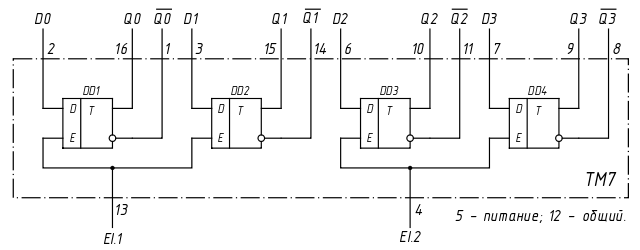

Микросхема ТМ7 содержит четыре D-триггера, входы синхронизации которых попарно соединены и обозначены как входы разрешения загрузки EI.

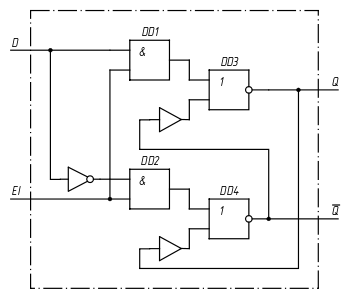

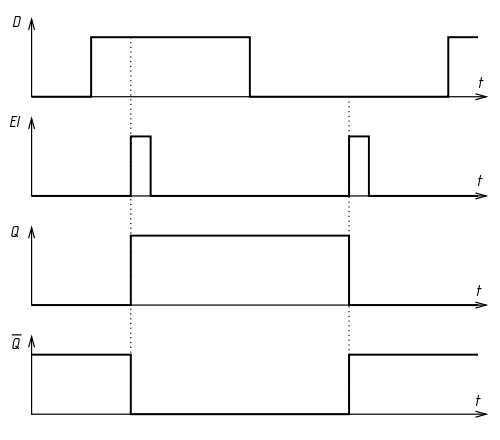

Если на такой вход разрешения EI подается напряжение высокого уровня, то информация, поступающая на входы D, попадает в триггеры и передаётся на их выходы.

При напряжении низкого уровня на входе разрешения EI в триггерах хранится то состояние, которое было на входах D на момент перехода сигнала на входе EI из высокого уровня в низкое (защёлкивание).

Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы Каждый триггер микросхемы имеет прямые Q и инверсные Q выходы.

Основные параметры микросхемы:

Напряжение питания: 5 В;

Выходное напряжение логического нуля <= 0,4 В;

Выходное напряжение логической единицы >= 2,4 В;

Входной ток логического нуля <= -3,2 мА (вх. 2, 3, 6, 7), -6.4 мА;

Входной ток логической единицы <= 0,16 мА;

Время распространения импульса при переходе 0 - 1 <= 25 нс;

Время распространения импульса при переходе 1 - 0 <= 30 нс;

Потребляемый от источника питания ток <= 53 мА.

Функциональная схема:

Структура D-триггера:

Временные диаграммы:

| Режим работы | Входы | Выходы | ||

|---|---|---|---|---|

| EI | D | Qn+1 | Qn+1 | |

| Разрешение передачи данных на выход | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | |

| Защёлкивание данных | 0 | * | Qn = 1 | Qn = 0 |