155ТМ7 — различия между версиями

Hdc (обсуждение | вклад) |

Hdc (обсуждение | вклад) |

||

| Строка 7: | Строка 7: | ||

Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы | Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы | ||

Каждый триггер микросхемы имеет прямые Q и инверсные {{Overline|Q}} выходы. | Каждый триггер микросхемы имеет прямые Q и инверсные {{Overline|Q}} выходы. | ||

| + | |||

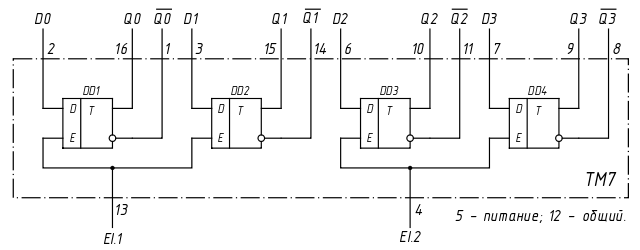

| + | Функциональная схема: | ||

| + | [[File:tm7.png]] | ||

Версия 09:04, 21 июля 2012

Микросхема ТМ7 содержит четыре D-триггера, входы синхронизации которых попарно соединены и обозначены как входы разрешения загрузки EI.

Если на такой вход разрешения EI подается напряжение высокого уровня, то информация, поступающая на входы D, попадает в триггеры и передаётся на их выходы.

При напряжении низкого уровня на входе разрешения EI в триггерах хранится то состояние, которое было на входах D на момент перехода сигнала на входе EI из высокого уровня в низкое (защёлкивание).

Такие триггеры используются в качестве четырехразрядного регистра хранения информации с непарным тактированием разрядов, а также в качестве буферной памяти и элемента задержки. Каждый триггер микросхемы Каждый триггер микросхемы имеет прямые Q и инверсные Q выходы.